## CubeRRT: CubeSat Radiometer Radio Frequency Interference Technology Validation

PI: Joel T. Johnson, The Ohio State University

## **Objective**

- Demonstrate wideband radio frequency interference (RFI) mitigating backend technology for future spaceborne microwave radiometers operating at 6 to 40 GHz

- Crucial to maintain US national capability for spaceborne radiometry and associated science goals

- Demonstrate real-time on-board RFI detection and mitigation in 1 GHz instantaneous bandwidth

- Enable development of future low data-rate radiometer systems with RFI-mitigation capability

- Demonstrate operations in space to elevate real-time on-board RFI processing technology to TRL 7

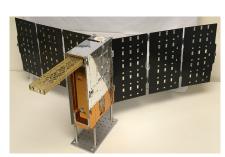

CubeRRT 6U spacecraft with solar panels and payload antenna deployed

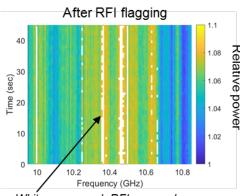

White areas mark RFI removed

CubeRRT spectrogram on 9/5/2018 showing on-board RFI filtering that reduces downlink data volume by 99%

## **Accomplishments**

- Designed, implemented, and demonstrated an on-board real-time RFI processor capable of observing a 1 GHz instantaneous bandwidth combined with tunable 6-40 GHz radiometer front end and antenna subsystems

- Through extensive pre-launch testing, RF electronics in a 2.5U, 2.5 kg package demonstrated NEDT performance of sub-kelvin level at less than 10 GHz and remaining < 3 K up to 30 GHz. This technology received the US patent in May 2020.

- On-board processor reduces 1 GHz input bandwidth into estimated power (brightness temperature) before and after RFI mitigation

using 128 frequency channel kurtosis and cross-frequency detection algorithms, and it achieves SWaP (~ 0.25 U, 170 g, 10 W) and

configurability which motivate adoption by future missions

- 6-40 GHz tri-element tapered helix antenna subsystem achieves gains from 7 to 21 dBi in 0.25U, 116 g package

- System launched to the ISS on 5/21/18, deployed from the ISS on 7/13/18, and operated through 6/30/20

- Collected "first light" data on September 5, 2018 that validated RFI filtering algorithms; on-board processor has since operated successfully for more than 5400 hours in space, exceeding project goals and reaching TRL 7

- Demonstrated the reliability of COTS Xilinx Zynq-7100 FPGA and TI ADC08D1520 ADC by two years of space operations

**Co-Is/Partners:** C. Chen, C. Ball, C. McKelvey, OSU; S. Misra, S. Brown, J. Kocz, R. Jarnot, JPL; K. Horgan, J. Lucey, J. Piepmeier, GSFC; D. Laczkowski, M. Pallas, N. Monahan, BCT

$$TRL_{in} = 5$$

$TRL_{out} = 7$